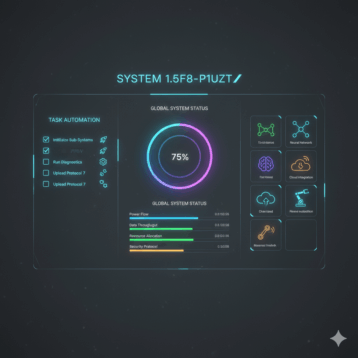

In partnership with the Fraunhofer Institute in Berlin, the IBM team demonstrated a prototype that incorporates the cooling system into the 3-D chips by piping water directly between each layer in the stack. The 3-D processor stacks chips and memory devices that conventionally sit side-by-side on a silicon wafer and stack them together on top of one another. This feat presents one of the most innovative methods for increasing microchip performance developed in recent years.

Placing chips vertically, rather than side by side, trims down the distance data has to travel, thus improving efficiency and saving critical space. “As we package chips on top of each other, we have found that conventional coolers attached to the back of a chip don’t scale,” said Thomas Brunschwiler from IBM’s Zurich Research Laboratory. “In order to exploit the potential of high-performance 3D chip stacking, we need interlayer cooling,” he explained further.

|

One of the main obstacles of manufacturing smaller and faster chips is heat; it is the result of the transfer of electrons through the tiny wires linking millions of components on a modern processor. As more components are added on to chips, the problems become worse. For example, Intel only recently introduced a processor with two billion transistors. Managing the heat originating from this processor and future ones is of permanent concern to microchip manufacturers.

As a result, researchers around the world are actively looking for the most efficient way to remove heat from the chip. In 2007, US scientists developed tiny wind engines that produced a “breeze” which consisted of charged particles, or ions, to cool computer chips. However, heat dissipation problems would be aggravated in IBM’s multi-story chips which are going to be implemented in future processors.

To avoid this, researchers piped water through sealed tubes just 50 microns (millionths of a metre) in diameter, between individual layers. Water is much more effective than air at absorbing heat and with a minute measure of liquid flowing through the system, the researchers saw considerable results. Pumping liquids through computers isn’t new. Early mainframe computers had water pumped around them.

|

Enthusiasts building high end gaming machines have also been modding their computers with water coolers and numerous researchers and companies have presented proposals for directly cooling chips with fluids. In 2003, Stanford University’s offshoot company, ‘Cooligy’ revealed its Active Micro-Channel Cooling (AMC) technology, which let fluids pass through hundreds of tiny channels on the upper shell of a chip. The technology was used in some versions of Apple’s Power Mac G5 desktop computer, released in 2004.

IBM has said its new micro water-cooling technology could reach the market within five years.

In 2007 TFOT covered another innovative processor cooling technology based on ionic wind developed by Kronos Advanced Technologies in collaboration with Intel and the University of Washington. TFOT has also previously written about the MIT team who developed an energy efficient microchip, where researchers discovered a way to significantly decrease microchip energy consumption to one tenth of the current rates. TFOT also covered the chip technology of cooler, faster, cheaper silicon chips recently developed using a new process and equipment that is expected to significantly reduce the amount of heat generated by silicon chips used for speeding processors.

Additional information of IBM’s water cooling system for 3-D chips can be found on IBM’s website.